# MACHXO2 入门开发板手册

| 文档版本号 | 更新内容              |

|-------|-------------------|

| V1.0  | 2021年6月5日创建       |

| V1.1  | 2023年8月1日修改图,增加按键 |

| V1.2  | 2024年3月6日 增加烧录细节  |

|       |                   |

|       |                   |

# 技术支持与反馈

深圳市飞录科技有限公司提供全方位技术支持,在使用过程中如有任何疑问或建议,可直接与公司联系:

网址: www.szfpga.com

E-mail: support@szfpga.com

# 目录

| 1. | 概述         | 4    |

|----|------------|------|

|    | 芯片说明       |      |

| 3. | 管脚说明       | 7    |

| 5. | 开机测试       | . 11 |

| 6. | 编译 Demo 程序 | . 12 |

| 7. | 下载运行       | . 14 |

| 8. | 包装信息       | . 19 |

| 9. | 订货信息       | . 20 |

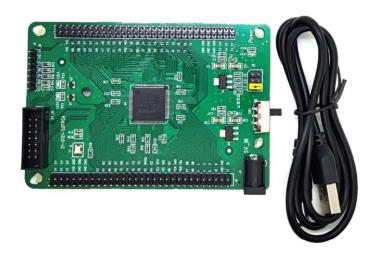

### 1. 概述

非常感谢选择 SZFPGA MACHXO2 入门开发板。

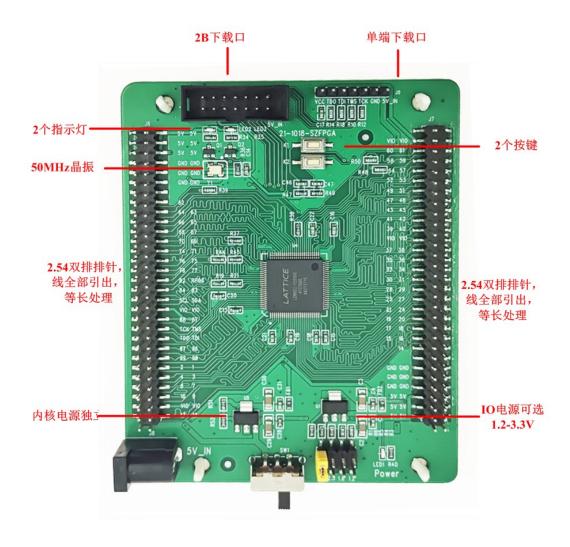

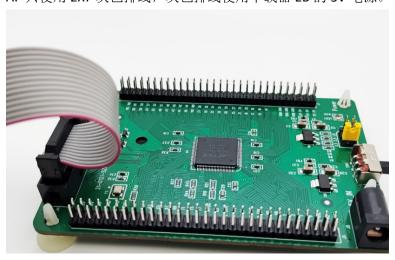

本手册描述怎么使用 MACHXO2 入门开发板,来测试和评估 LATTICE 厂家 MACHXO2 的芯片。开发板最大化程度,可以方便定制自己产品和方案。

LATTICE 是一家老牌的 FPGA 厂家。在 CPLD 和 FPGA 低成本,小封装独树一帜。特别在消费电子,小型化设备,控制领域用的比较多。

MACHXO2 入门开发板芯片型号为 MACHXO2 入门开发板采用 Lattice 的 MACHXO2 家族系列芯片,LCMXO2-1200HC 或者 LCMXO2-2000HC CPLD 芯片。MACHXO2 系列芯片具有低功耗,瞬时启动,高安全性,低成本,内置 SPI/I2C,内置用户 Flash 等特点。

MACHXO2 入门开发板提供 MACHXO2 基本功能电路,引出所有 IO 口。并且将 IO 数据线 缆已经做了等长处理。其中 VCC 和 VCCIO 电源是独立,可以兼容 ZE 和 HC 芯片功能。而 VCCIO 电源支持多个电源,选择从 1.2V、1.8、2.5、3.3V。

MACHXO2 入门开发板设计,兼容 MACHXO2 LQFP100 封装,从型号 640HC 到 2000HC 系 类。HC 和 ZE 同样可以换,只需要改修 VCC 电压即可。

#### MACHXO2 入门开发板特性:

- 主芯片: LCMXO2-1200HC 或者 LCMXO2-2000HC。

- 内置配置 Flash, 无需外部配置芯片。

- 内核,辅助电源, IO 电源独立。

- VCCIO 电源多个选择, 1.2V、1.8V、2.5V、3.3V, 无需电平转换芯片。

- 全部 IO 引脚引出,并在引脚座标记,方便操作识别

- 全部 IO 做等长处理,芯片时序保证。

- 芯片内置晶振。

- 板载晶振 50M, 宽电压支持 1.8-3.3V。

- 2 个 LED。

- 电源 DC5.2mm 接口,结实耐用。

- 低功耗, USB 转 DC 5V 供电。

- 多个下载口,单排下载口以及冗余 2B 下载口。

### 2. 芯片说明

芯片型号为 LCMXO2-1200HC 或者 LCMXO2-2000HC,LQFP100 封装,封装是 LQFP100,从 640HC 到 2000HC 芯片资源如下表所示。XO2-1200 资源 LUT 1280,包含一个 PLL,7 个 9Kb 的 EBR。XO2-2000HC,资源 LUT 2112,一个 PLL,8 个 9Kb 的 EBR。

MachXO2 内置晶振,频率可从 133-2.08 范围内。

MachXO2 的全系列芯片都是自带硬核 I2C,SPI, Timer, 用户 Flash,可以用于电机控制产品。硬核总线是通过 WISHBONE 总线控制线,详见手册<Using User Flash Memory and Hardened Control Functions in MachXO2 Devices>。

WOO WOO WOO WOO WOO WOO WOO

|                                                     |                  | XO2-     | XO2- | XO2-              | XO2- | XO2-               | XO2- | XO2-               | XO2-      | XO2- |

|-----------------------------------------------------|------------------|----------|------|-------------------|------|--------------------|------|--------------------|-----------|------|

|                                                     |                  | 256      | 640  | 640U <sup>1</sup> | 1200 | 1200U <sup>1</sup> | 2000 | 2000U <sup>1</sup> | 4000      | 7000 |

| LUTs                                                |                  | 256      | 640  | 640               | 1280 | 1280               | 2112 | 2112               | 4320      | 6864 |

| Distributed RAM (kbits)                             |                  | 2        | 5    | 5                 | 10   | 10                 | 16   | 16                 | 34        | 34   |

| EBR SRAM (Kbits)                                    |                  | 0        | 18   | 64                | 64   | 74                 | 74   | 92                 | 92        | 240  |

| Number of EBR SRAM E                                | Blocks (9 Kbits) | 0        | 2    | 7                 | 7    | 8                  | 8    | 10                 | 10        | 26   |

| UFM (kbits)                                         |                  | 0        | 24   | 64                | 64   | 80                 | 80   | 96                 | 96        | 256  |

|                                                     | HC <sup>2</sup>  | Yes      | Yes  | Yes               | Yes  | Yes                | Yes  | Yes                | Yes       | Yes  |

| Device Options:                                     | HE <sup>3</sup>  |          |      |                   |      |                    | Yes  | Yes                | Yes       | Yes  |

|                                                     | ZE <sup>4</sup>  | Yes      | Yes  |                   | Yes  |                    | Yes  |                    | Yes       | Yes  |

| Number of PLLs                                      |                  | 0        | 0    | 1                 | 1    | 1                  | 1    | 2                  | 2         | 2    |

|                                                     | I <sup>2</sup> C | 2        | 2    | 2                 | 2    | 2                  | 2    | 2                  | 2         | 2    |

| Hardened Functions                                  | SPI              | 1        | 1    | 1                 | 1    | 1                  | 1    | 1                  | 1         | 1    |

|                                                     | Timer/Counter    | 1        | 1    | 1                 | 1    | 1                  | 1    | 1                  | 1         | 1    |

| Packages                                            | Timery counter   |          | -    | -                 | -    | 1/0                | -    | -                  | -         | _    |

| 25-ball WLCSP <sup>5</sup>                          |                  | Ī        | 1    | Ī                 |      |                    | I    | l                  | I         |      |

| (2.5 mm x 2.5 mm, 0.4                               | mm)              |          |      |                   | 18   |                    |      |                    |           |      |

| 32 QFN <sup>6</sup>                                 | ,                | 1 2      |      |                   |      |                    |      |                    | 2         |      |

| (5 mm x 5 mm, 0.5 mm                                | 1                | 21       |      |                   | 21   |                    |      |                    |           |      |

| 36-ball WLCSP <sup>5</sup>                          | ,                |          |      | 5                 |      |                    | 100  |                    | 1         |      |

| (2.5 mm x 2.5 mm, 0.4                               | mm)              |          |      |                   | 28   |                    |      |                    |           |      |

| 48 QFN <sup>8, 9</sup>                              | ,                |          |      |                   |      | <b>-</b>           |      |                    |           |      |

| (7 mm x 7 mm, 0.5 mm)                               |                  | 40       | 40   |                   |      |                    |      |                    |           |      |

| 49-ball WLCSP <sup>5</sup>                          | ,                | <u> </u> |      | 86                |      |                    |      | 2                  |           | 2    |

| (3.2 mm x 3.2 mm, 0.4 mm)                           |                  |          |      |                   |      |                    | 38   |                    |           |      |

| 64-ball ucBGA                                       |                  |          |      |                   |      |                    |      |                    |           |      |

|                                                     |                  | 44       |      |                   |      |                    |      |                    |           |      |

| (4 mm x 4 mm, 0.4 mm)<br>81-ball WLCSP <sup>5</sup> |                  | 2        |      | 86                |      |                    |      |                    | S. Carlos | 2    |

| (3.8 mm x 3.8 mm, 0.4                               | mm)              |          |      |                   |      |                    |      |                    | 63        |      |

| 84 QFN <sup>7</sup>                                 | ,                |          |      |                   |      |                    |      |                    |           |      |

| (7 mm x 7 mm, 0.5 mm                                | )                |          |      |                   |      |                    |      |                    | 68        |      |

| 100-pin TQFP                                        | ,                | 1        |      | 33                | /    |                    |      | 8                  | 2         | 8    |

| (14 mm x 14 mm)                                     |                  | 55       | 78   |                   | 79   |                    | 79   |                    |           |      |

| 132-ball csBGA                                      |                  |          |      |                   |      |                    | ,    |                    |           |      |

| (8 mm x 8 mm, 0.5 mm                                | )                | 55       | 79   |                   | 104  |                    | 104  |                    | 104       |      |

| 144-pin TQFP                                        | ,                |          |      | 4                 | /    |                    |      |                    | -         |      |

| (20 mm x 20 mm)                                     |                  |          |      | 107               | 107  |                    | 111  |                    | 114       | 114  |

| 184-ball csBGA7                                     |                  |          |      |                   |      |                    |      |                    |           |      |

| (8 mm x 8 mm, 0.5 mm)                               |                  |          |      |                   |      |                    |      |                    | 150       |      |

| 256-ball caBGA                                      |                  |          |      |                   |      |                    | 4    |                    |           |      |

| (14 mm x 14 mm, 0.8 mm)                             |                  |          |      |                   |      |                    | 206  |                    | 206       | 206  |

| 256-ball ftBGA                                      |                  |          |      |                   |      | 4                  | 1    |                    |           |      |

| (17 mm x 17 mm, 1.0 mm)                             |                  |          |      |                   |      | 206                | 206  |                    | 206       | 206  |

| 332-ball caBGA                                      |                  | 1        |      |                   |      | 1                  |      |                    | 4         |      |

| (17 mm x 17 mm, 0.8 n                               | nm)              |          |      |                   |      |                    |      |                    | 274       | 278  |

| 484-ball ftBGA                                      |                  |          |      |                   |      |                    |      | 4                  | 1         |      |

| (23 mm x 23 mm, 1.0 mm)                             |                  | 1        | I    | 1                 | 1    | I                  | 1    | 278                | 278       | 334  |

封装从最小的 wlcsp25 到最大的 484FTBGA 封装。Machxo2 内置 8:1 的同步源端,可以用 DDR,DDR2,LPDDR 接口。支持 7:1 模式,可以用 LVDS 显示屏接口转换。

### 3. 管脚说明

### 1) LED 说明

| 功能   | 方向 | FPGA 引脚 |

|------|----|---------|

| LED0 | 输入 | 76      |

| LED1 | 输出 | 60      |

#### 2) 晶振

| 功能    | 方向 | FPGA 引脚 |

|-------|----|---------|

| 50MHz | 输入 | 63      |

#### 3) 按键

| 功能   | 方向 | FPGA 引脚 |

|------|----|---------|

| KEY0 | 输入 | 58      |

| KEY1 | 输入 | 59      |

### 4)排针连接

2 个 2\*30P 的双排排针,将所有的 IO 引出。并且,板上丝印已经注明 IO 管脚功能名称。注意,排针输出和板子上其他的功能是复用。IO 前缀代表是 FPGA 管脚位置。

#### J6 连接器引脚说明

| IO 名称 | 功能引脚 | IO 名称 | 功能引脚 |

|-------|------|-------|------|

| 1     | 5V   | 2     | 5V   |

| 3     | 5V   | 4     | 5V   |

| 5     | 5V   | 6     | 5V   |

| 7     | GND  | 8     | GND  |

| 9     | GND  | 10    | GND  |

| 11    | GND  | 12    | GND  |

| 13    | NC   | 14    | NC   |

| 15    | IO62 | 16    | NC   |

| 17    | IO64 | 18    | IO63 |

| 19    | 1066 | 20    | IO65 |

| 21    | IO68 | 22    | 1067 |

| 23    | 1070 | 24    | 1069 |

| 25 | 1074  | 26 | 1071    |

|----|-------|----|---------|

| 27 | IO76  | 28 | 1075    |

| 29 | IO78  | 30 | 1077    |

| 31 | 1082  | 32 | PROGRAM |

| 33 | 1084  | 34 | 1083    |

| 35 | SCL   | 36 | SDA     |

| 37 | VCCIO | 38 | VCCIO   |

| 39 | IO88  | 40 | 1087    |

| 41 | TCK   | 42 | TMS     |

| 43 | TDO   | 44 | TDI     |

| 45 | 1097  | 46 | 1096    |

| 47 | 1099  | 48 | 1098    |

| 49 | 102   | 50 | IO1     |

| 51 | 104   | 52 | 103     |

| 53 | 108   | 54 | 107     |

| 55 | IO10  | 56 | 109     |

| 57 | VCCIO | 58 | VCCIO   |

| 59 | IO13  | 60 | IO12    |

#### J7 连接器引脚说明

| IO 名称 | 功能引脚  | IO 名称 | 功能引脚  |

|-------|-------|-------|-------|

| 1     | 5V    | 2     | 5V    |

| 3     | 5V    | 4     | 5V    |

| 5     | 5V    | 6     | 5V    |

| 7     | GND   | 8     | GND   |

| 9     | GND   | 10    | GND   |

| 11    | GND   | 12    | GND   |

| 13    | NC    | 14    | NC    |

| 15    | IO14  | 16    | NC    |

| 17    | IO16  | 18    | IO15  |

| 19    | IO18  | 20    | IO17  |

| 21    | 1020  | 22    | IO19  |

| 23    | 1024  | 24    | IO21  |

| 25    | 1027  | 26    | 1025  |

| 27    | 1029  | 28    | IO28  |

| 29    | IO31  | 30    | 1030  |

| 31    | 1034  | 32    | 1032  |

| 33    | 1036  | 34    | 1035  |

| 35    | 1038  | 36    | 1037  |

| 37    | VCCIO | 38    | VCCIO |

| 39    | 1040  | 40    | IO39  |

| 41    | 1042  | 42    | IO41  |

| 43    | 1045  | 44    | IO43  |

| 45 | IO48  | 46 | IO47  |

|----|-------|----|-------|

| 47 | IO51  | 48 | IO49  |

| 49 | 1053  | 50 | IO52  |

| 51 | 1057  | 52 | IO54  |

| 53 | 1059  | 54 | IO58  |

| 55 | IO61  | 56 | 1060  |

| 57 | VCCIO | 58 | VCCIO |

| 59 | NC    | 60 | NC    |

# 4. 软件开发

开发软件使用 Diamond。

diamond 下载软件地址:

https://pan.baidu.com/s/15TLVFNUvzoKJOxgxPiGi7A 提取码: qtm4 提取码: qtm4

或者上 lattice 公司网站下载

https://www.latticesemi.com/Products/DesignSoftwareAndIP/FPGAandLDS/LatticeDiamond

### 5. 开机测试

入门开发板在出厂前,已将测试程序下载到内部,接通电源即可检查开发板是否正常。确保 J9 VIO 电源跳线确保短接,并且在设定电源。

连接好 USB 转 DC 电源线,插上电源,可以显示单个灯交替闪烁。

### 6. 编译 Demo 程序

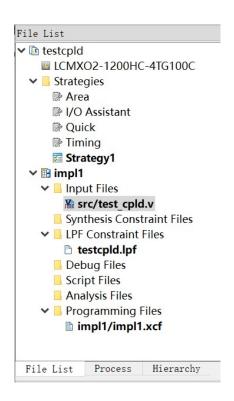

通过 Diamond 打开开发板资料中 code\testcpld - 1200hc 目录下 testcpld,并对工程进行编译。注意工程要在英文目录,不要带中文路径上。

- 1) 打开 testcpld.ldf 工程,在"File List"窗口中显示如下信息,其中:

- ◆ LCMXO2-1200HC-4TG100C: Lattice MACHXO2 型号;

- ◆ test\_cpld.v: Verilog 代码;

- ◆ testcpld.lpf: 物理约束文件。

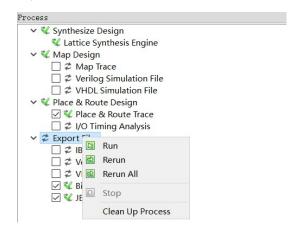

2) 切换到"Process"窗口,确定勾选选择 JEDEC File 和 Bitstream File,选择 Export Files,在 Export Files 右键选择 Rerun All

- - ✓ **W** Bitstream File

- ✓ ¥ JEDEC File

### 7. 下载运行

1) 将下载器连通开发板和 PC 机, 打开电源开关,

连接模式有两种:

A. 只使用 2X7 灰色排线,灰色排线使用下载器 2B 的 5V 电源。

B. 使用 DC 和单端线缆。此类可以兼容其他的 2A 下载器。2B 下载器线缆也可以支持。 DC 插入电源电压是 5V, 线缆根据定义插入, VCC, TDO, TDI, TMS, TCK, GND。

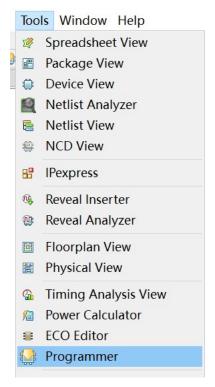

2) 在 Diamond 中"Tools"菜单中,选择"Programmer",

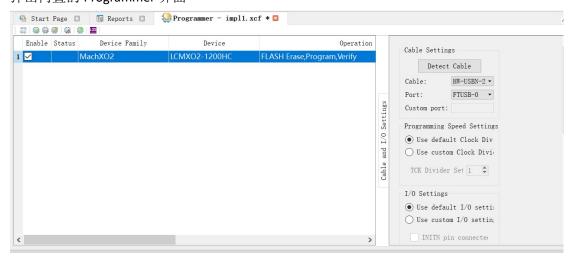

#### 弹出内置的 Programmer 界面

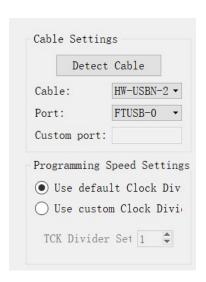

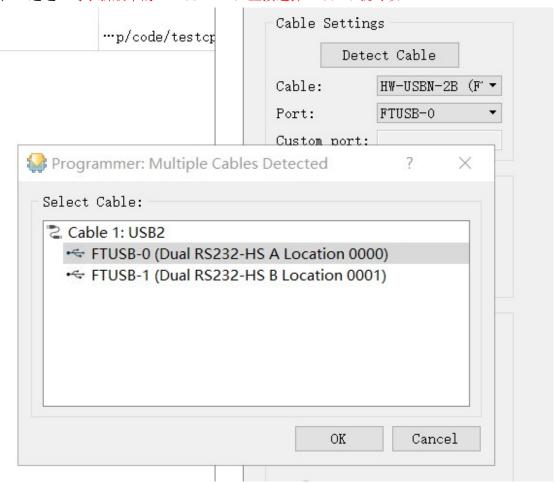

3) 在右边栏目 Cable Settings 中选择,Detect Cable

注意:在 Windows10由于串口初始化,会导致 FTUSB-0和 FTUSB-1顺序错误,必须确认在 A 通道。对于新版本的 HW-USBN-2B,直接选择 FTUSB-0就可以。

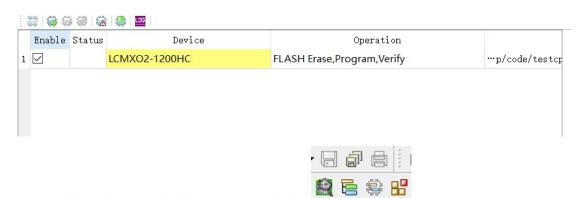

2)首先可以点 Scan 扫描芯片,找到开发板是否存在芯片。

出现黄色,请点击这个黄色名称,然后保存。

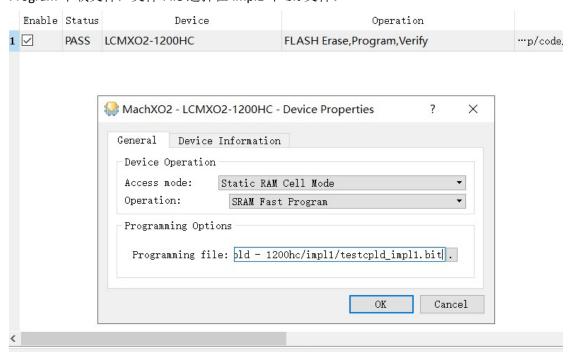

3)在 Operation 双击,弹出对话框,选择 Static RAM Cell Mode 操作模式,SRAM Fast Program 下载文件,文件 File 选择在 impl1 中 bit 文件。

4)下载文件,点击绿色按钮

```

Output

INFO - Check configuration setup: Start.

INFO - JTAG Chain Verification. No Errors.

INFO - Check configuration setup: Successful.

INFO - Devicel LCMXO2-1200HC: SRAM Fast Program

INFO - Operation Done. No errors.

INFO - Elapsed time: 00 min: 03 sec

INFO - Operation: successful.

```

#### 5) 显示效果, 灯闪烁

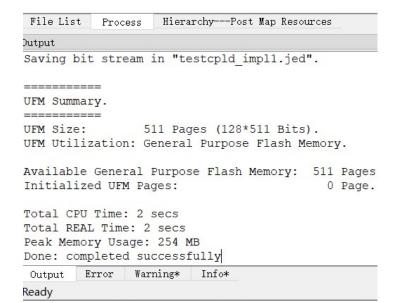

#### 6) 烧录 JED

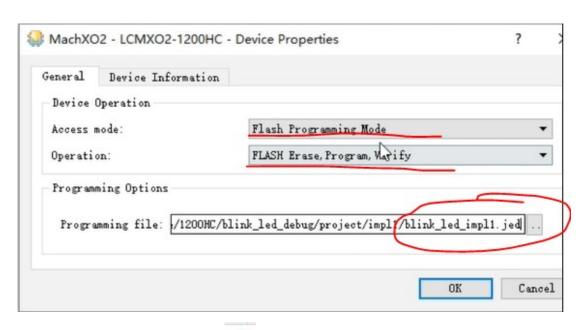

对于 SRAM, 断电是会消失的, 所以烧录要 jed 文件, 可以保存在 FPGA 内部的配置文 件中。选择 operation 中,Access mode 选择 flash progarmming mode。在 operation 中选择 FIASH Erase,program,Verify。在 programming file 选择 jed 的文件。

4)下载 Jed 文件,点击绿色按钮 \_\_\_\_\_,完成这个 jed 文件烧录。

# 8. 包装信息

- 1) MACHXO2 入门开发板

- 2) USB 转 DC5.2mm 线缆

# 9. 订货信息

| 产品名称               | 备注                           |

|--------------------|------------------------------|

| MACHXO2 入门开发板 1200 | 主芯片型号是 LCMXO2-1200HC-4TG100C |

| MACHXO2 入门开发板 2000 | 主芯片型号是 LCMXO2-2000HC-4TG100C |